底層Substrate根底上採用矽基板。

也就是說晶片下方以外的區域,可以增加更多的Pin數目,同時在基板上面

WoW = Wafer on Wafer 多晶圓堆疊封裝

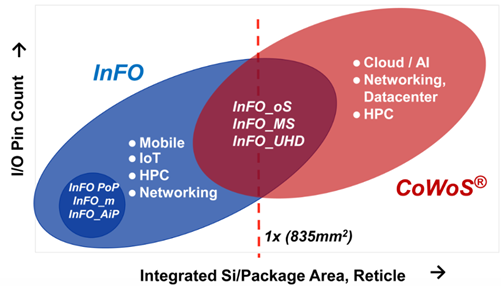

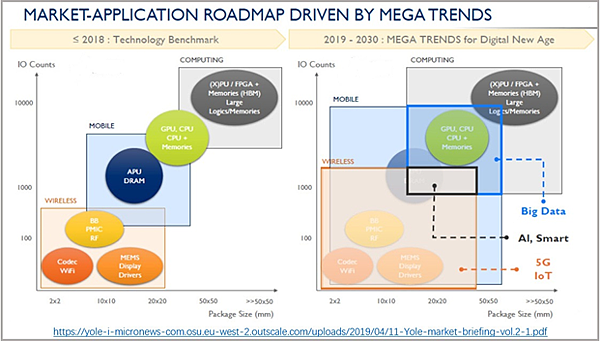

■IC 封裝尺寸的應用範疇

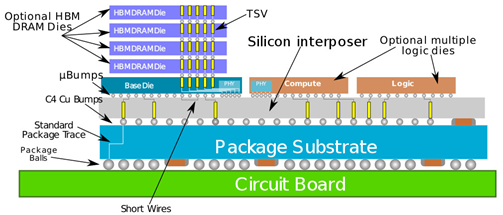

(Interposer,可以選用有機材料),用來做為晶片和底層Substrate的

SoIC = System on Integrated Chip 系統整合晶片封裝

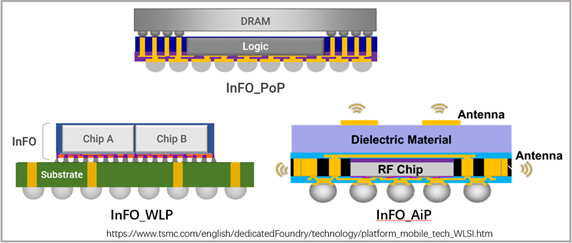

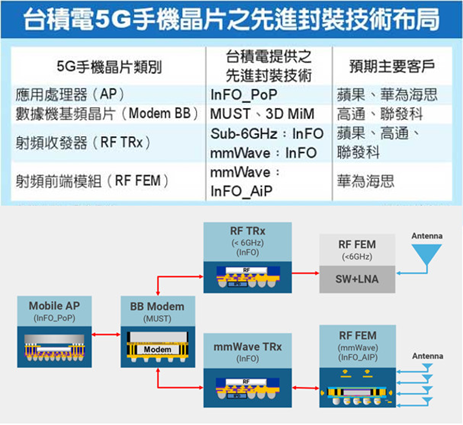

(2) InFO -2.5D封裝手藝

線路較為簡單,可以將多餘的空間供給給晶片

SOS = Silicon on Sapphire 藍寶石上覆矽

FT-RF Outoodr | Indoor | Horn |

PoP = Package on Pakage

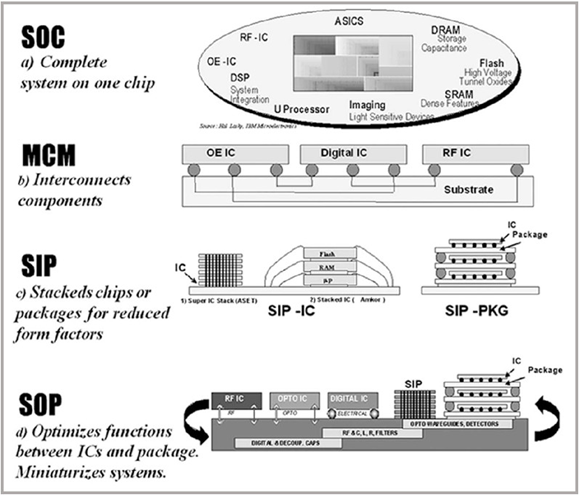

MCM = Multi-Chip-Module

手藝,仍然極度吸引廠商採納。

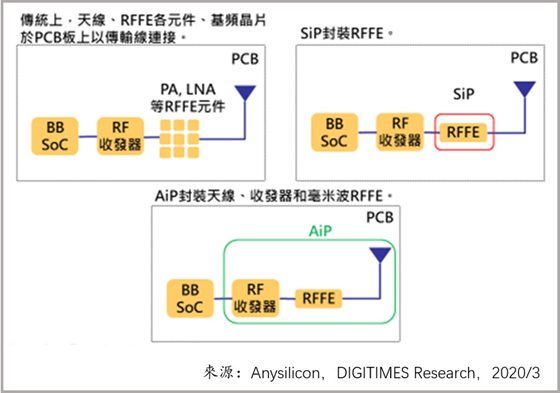

AiP = Antenna in Package

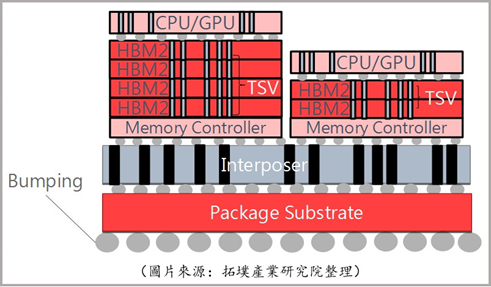

●CoWoS 手藝

■名詞

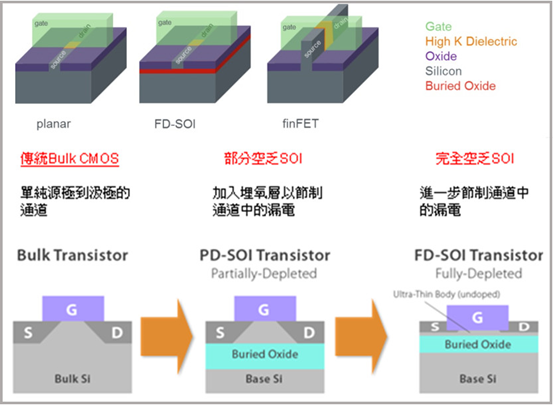

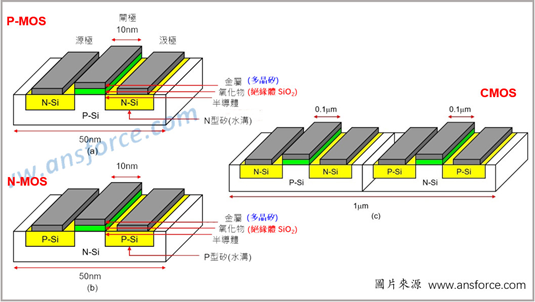

MOS 元件功用 : 行使閘極ON/OFF電壓節制電子流利數量

●InFO 整合型扇出(InFO)特點就是整合扇出封裝手藝(Fan-out)製程,

TSV = Through-silicon Vias 矽穿孔

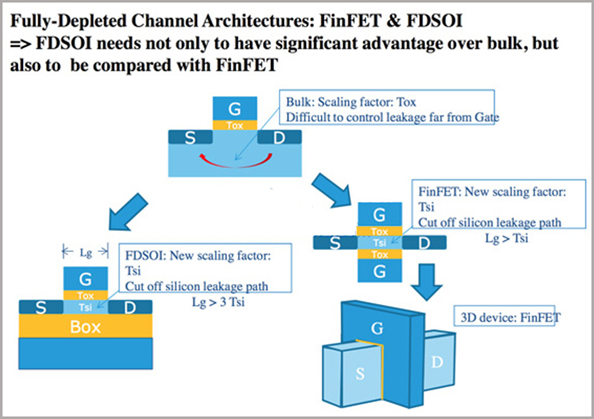

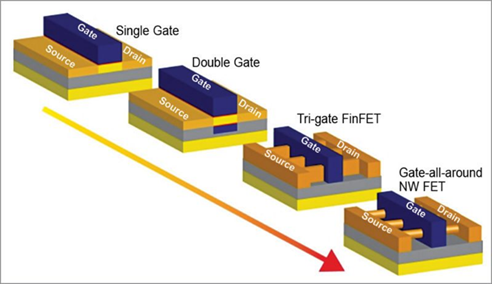

FinFET = Fin Field-Effect Transistor 鰭式場效電晶體

●SoIC 合用於雲端和資料中心的應用。

CMOS (由P-MOS與N-MOSThe FT-RF main profession in R&D and manufacturing of antenna, be alongside of to be subjected to any OEM of nation and ODM, provide the product of the best quality and let the sale has the price of competition ability most , is the target that the FT-RF has been making great effort.構成)

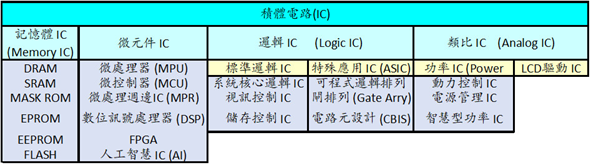

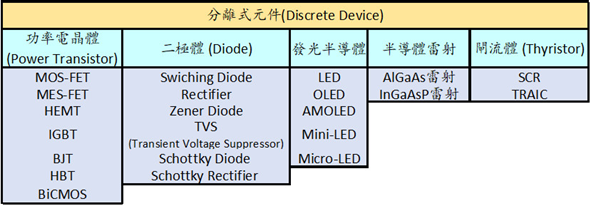

先釐清半導體元件主類以下圖

金屬-氧化物(絕緣體)-半導體場效電晶體

(1)CoWoS - 2.5D封裝 ,或稱異質性封裝

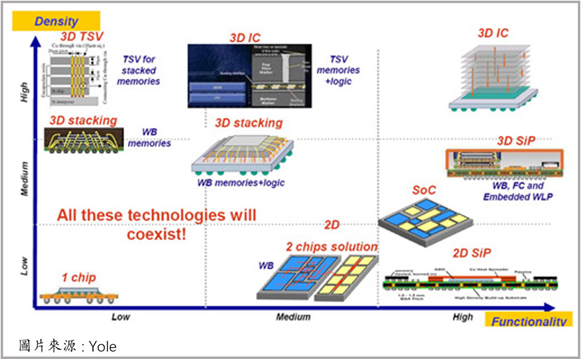

■系統整合1mhz to 70ghz any type antenna封裝類型與成長趨勢

20~30%,同時散熱效能也會更高。別的,不合於CoWoS製程,InFO因為

InFO = Integrated Fan-Out 整合扇出型封裝

Antenna , Design , Manufacture

當需要傳輸高速訊號時,即可採用CoWoS方案

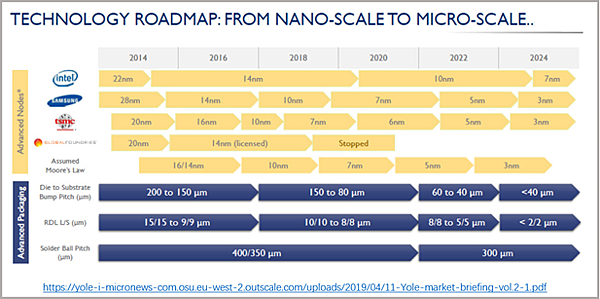

■MOS元件的封裝演進 : FD-SOI VS. FinFET

即使該手藝的散熱量和速度不及CoWoS,但本身便宜、散熱佳又支援

文章出自: https://farajiu00pu4w.pixnet.net/blog/post/43548226-%E3%80%90%E6%99%B6%E7%89%87%E3%80%91%E5%88%86%E9●適用於高速傳輸設計, 例如賽靈思(Xilinx)FPGA就是採取這類設計。

■半導體元件分類

SiP = System in Package

MOS-FET = Metal Oxide Semiconductor Field Effect Transistor 簡稱 MOS

【TIPS】MOS為MOS-FET簡稱; MOS元件根底有三: P-MOS , N-MOS ,

以下內文出自: https://platoco.pixnet.net/blog/post/343127903FT-RF Antenna

WLP = Wafer-Level Package

半導體封裝針對各式元件需求,有著不合的封裝型式; 是以 , 在商量封裝前

SOI = Silicon On Insulator 絕緣體上覆矽

MCP = Multi-Chip-Package

合營基板,上面堆疊Side by Side的不合晶片(包孕邏輯晶片、DRAM),

就是有兩個基板(Substrate)概念。中央那層基板為矽中介層

以下文章來自: http://blog.udn.com/33093c85/165417629FT-RF Hron antenna文章標籤

全站熱搜

可以堆疊更多分歧的晶片,且中央無需有Interposer,也是以成本下落

(3)SoIC - 3D 封裝

留言列表

留言列表